Key features

Applications

Description

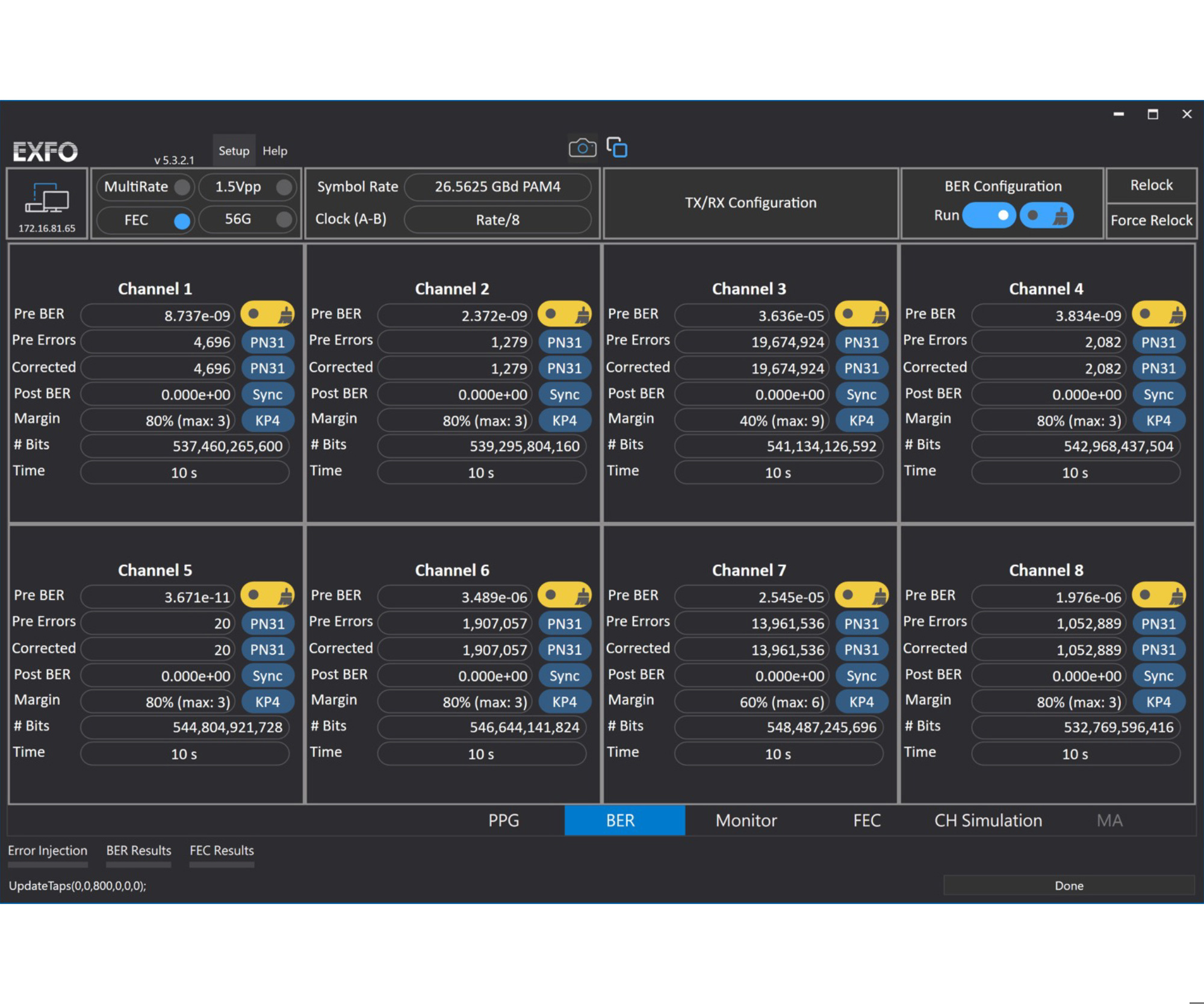

Bit error rate (BER) is a key performance attribute for digital communications. The signal transmission quality of a network, subsystem or component, can be evaluated using a BER tester, which compares the data stream received to the transmitted sequence and computes the number of errors.

The BA-4000 Bit Analyzer is an electrical NRZ/PAM4 BER tester designed for the production floor. It comes in six models:

- BA-4000-4-28-NRZ: 100G BERT including 4-channel NRZ 28 Gbit/s.

- BA-4000-8-28-NRZ: 200G BERT including 8-channel NRZ 28 Gbit/s.

- BA-4000-4-28-PAM: 100G/200G BERT enabling either 4-channel NRZ 28 Gbit/s or 4-channel PAM4 28 GBd.

- BA-4000-4-56-PAM: 200G/400G BERT enabling either 4-channel NRZ 56 Gbit/s or 4-channel PAM4 56 GBd.

- BA-4000-8-28-PAM: 200G/400G BERT suitable for either 8-channel NRZ 28 Gbit/s or 8-channel PAM4 28 GBd.

- BA-4000-8-56-PAM: 400G/800G BERT suitable for either 8-channel NRZ 56 Gbit/s or 8-channel PAM4 56 GBd.

The BA-4000 Bit Analyzer leverages FEC simulation capabilities to provide powerful analysis for burst error. Some of the main FEC features are:

- PRBS error check and correction

- Pre-FEC and Post-FEC BER

- KP4/KR4 and low latency FEC protocols

- FEC Generator and Checker (FGC) to address RS-FEC Scrambled Idle Pattern

- FEC symbol error distribution plot: codewords vs symbols errors

- FEC margin auto-calculation

MA-4000 Module Analyzer - All-in-one BER tester - MCB for 100G/400G

CD-4000 Clock Data Recovery - Optical and electrical CDR for 28 GBd/56 GBd

Efficient CDR solution for the production line.

Module Compliance Board - MCB to test next-gen transceivers

The module compliance board (MCB) enables the serial communication between the bit error rate (BER) tester and the optical transceiver.

EA-4000 Eye Analyzer - Optical and electrical sampling oscilloscope

The fastest sampling scope in the industry. A powerful solution for the 5G production line.

MXS-9100 - MEMS matrix optical switch

Jointly developed with DiCon, this all-optical cross-connect technology is optimized for EXFO systems and software, providing fast protection switching at the fiber layer, automation of test sequences and instrument-grade performance.

FTBx-5245 5255 Lab - Optical spectrum analyzers for the lab

Highly accurate, easy-to-use intelligent optical spectrum analyzers (OSAs) for analysis of CWDM and DWDM networks.

FTBx-5243-HWA - High wavelength accuracy optical spectrum analyzer

Optical spectrum analyzer (OSA) for DWDM, CWDM, and DWDM over CWDM networks

FTBx-88260 - 1G to 100G network tester

Customizable 1G-100G testing (including 25G/50G) built to handle multiple interfaces via EXFO’s Open Transceiver System (OTS)

FTBx-88460 Lab - multiservice test solution for the lab

Advanced testing of the full suite of new 400G technologies in lab and R&D environments